# Exploiting Task-Order Information

## for Optimizing Sequentially Consistent Java Programs

Christoph M. Angerer Thomas R. Gross ETH Zurich, Switzerland

## Sequential Consistency

- Easy-to-understand memory model

- Conceptually:

- All memory accesses are visible immediately

- All tasks agree on same legal sequential history of memory events

- No re-ordering

## Sequential Consistency

- Easy-to-understand memory model

- Conceptually:

- All memory accesses are visible immediately

- All tasks agree on same legal sequential history of memory events

- No re-ordering

Inefficient without optimizations!

Initially,

$$x == y == 0$$

1:

$$r1 = x$$

;

$$2: y = 2;$$

1:

$$r1 = x$$

; 3:  $r2 = y$ ;

Is

$$r1 == 1$$

AND  $r2 == 2$  possible?

Initially,

$$x == y == 0$$

```

1: r1 = x; 3: r2 = y;

2: y = 2; 4: x = 1;

```

Is r1 == 1 AND r2 == 2 possible?

Initially,

$$x == y == 0$$

Is r1 == 1 AND r2 == 2 possible?

Initially,

$$x == y == 0$$

Is r1 == 1 AND r2 == 2 possible?

No, if "sequentially consistent"

Initially,

$$x == y == 0$$

1:

$$r1 = x$$

$$4: x = 1;$$

1:

$$r1 = x$$

; 3:  $r2 = y$ ;

Is r1 == 1 AND r2 == 2 possible?

Yes, if the compiler reorders 1/2 and/or 3/4

- Simple model:

- Guard every memory access with barriers (fields and array elements)

- Simple model:

- Guard every memory access with barriers (fields and array elements)

- Drawbacks:

- Barriers introduce overhead

- Prevents many standard optimizations

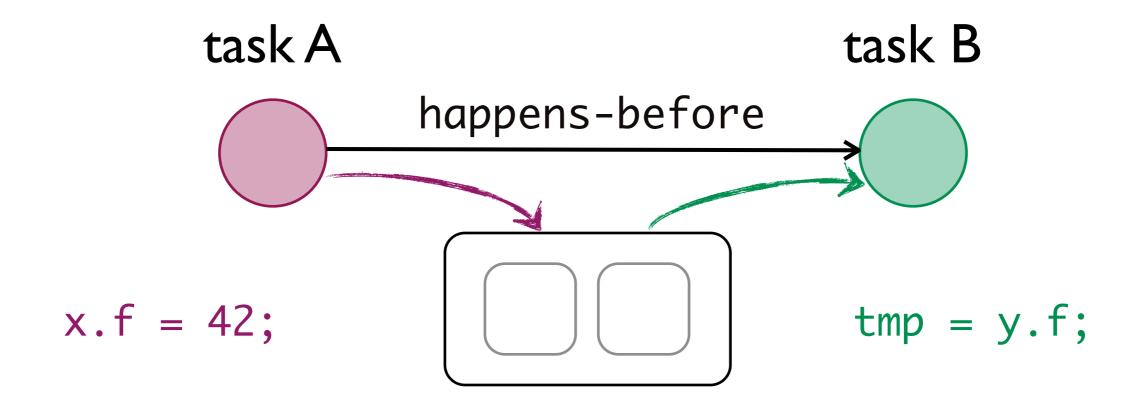

- Simple model:

- Guard every memory access with barriers (fields and array elements)

- Drawbacks:

- Barriers introduce overhead

- Prevents many standard optimizations

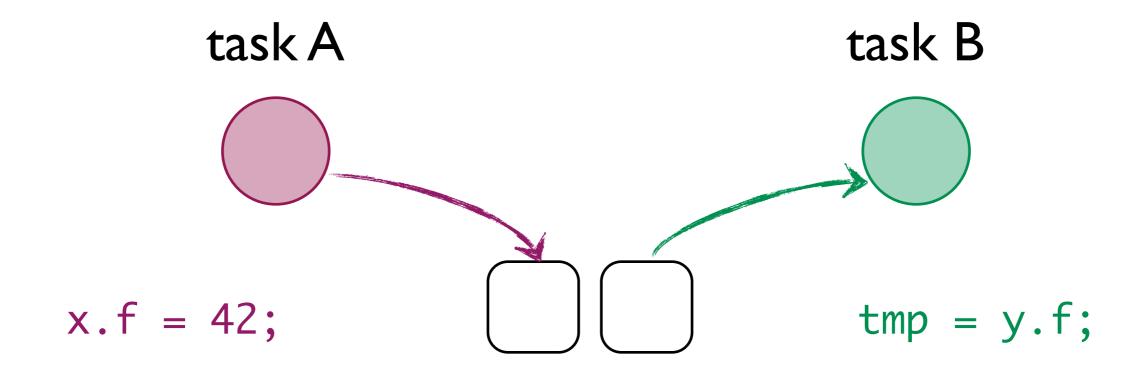

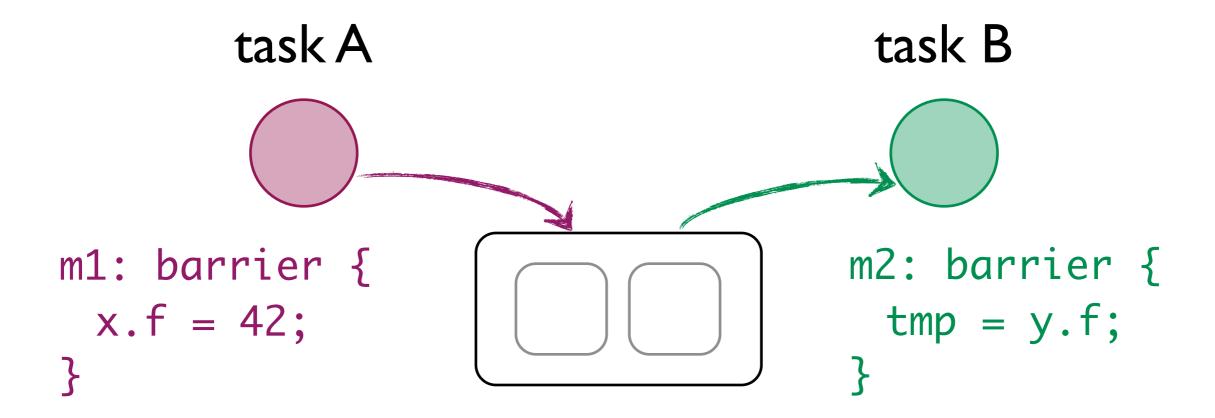

- Optimize to re-gain performance:

- Remove barriers where no parallel task may interfere

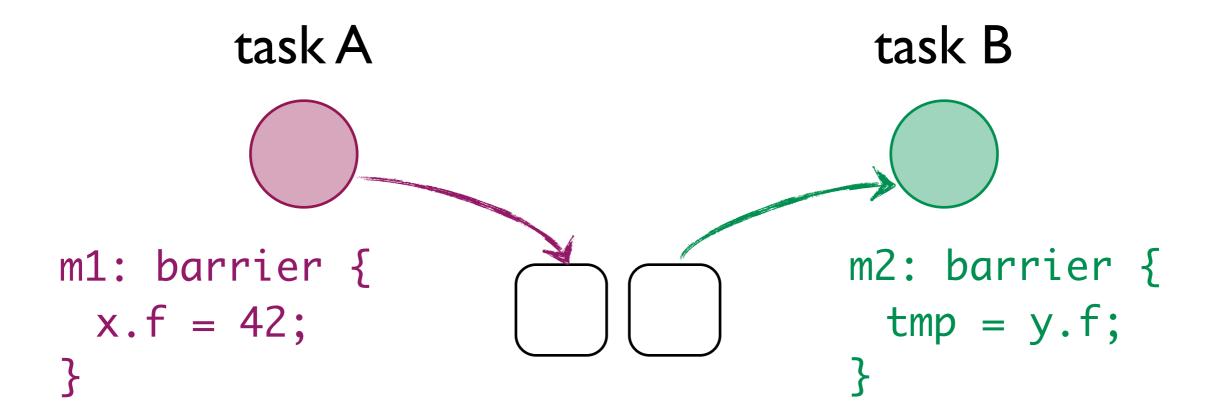

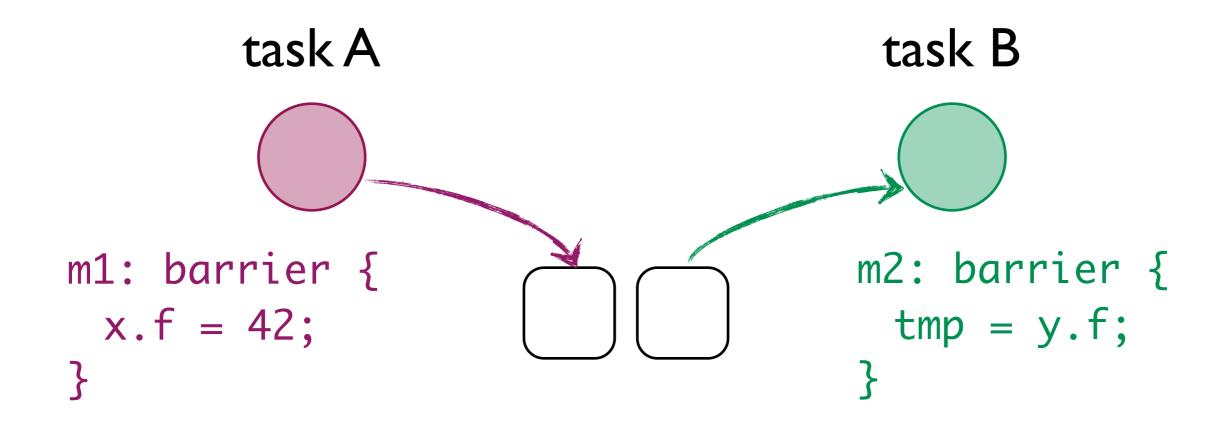

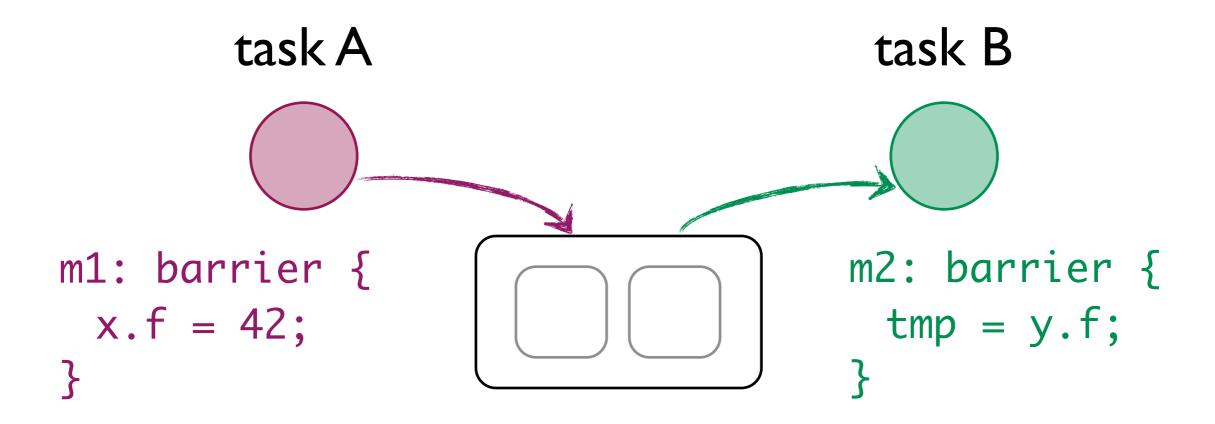

```

task A

m1: barrier {

x.f = 42;

}

```

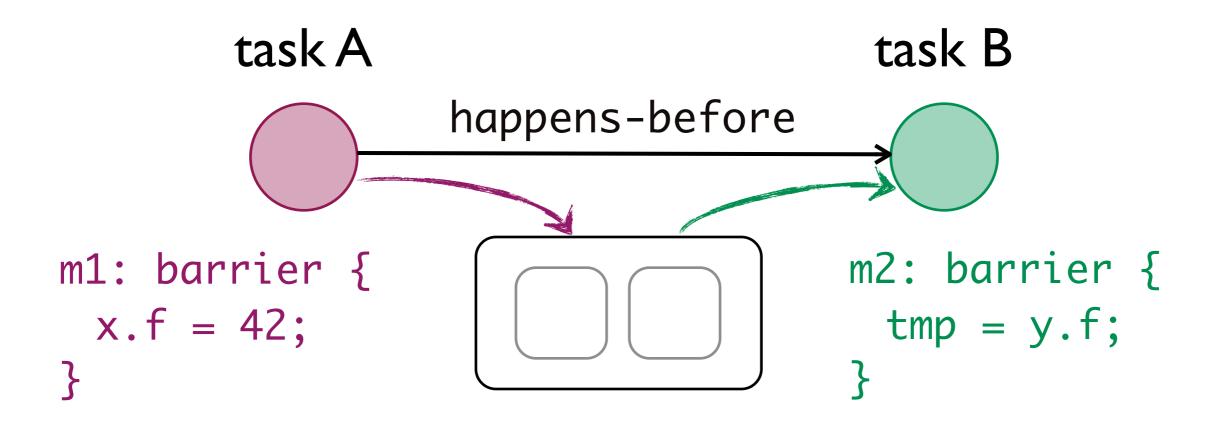

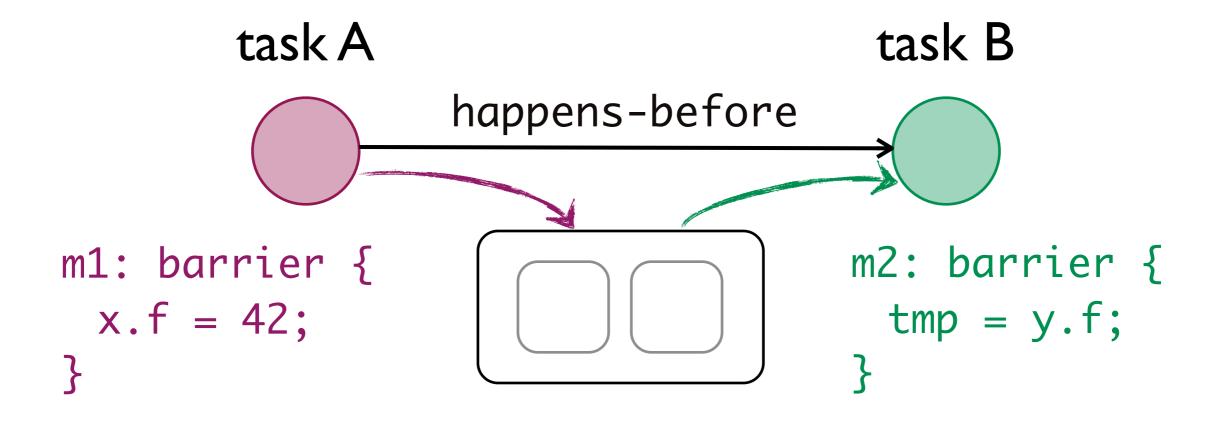

Can memory access m1 interfere with m2?

✓ Different Objects

Can memory access m1 interfere with m2?

✓ Different Objects

Can memory access m1 interfere with m2?

Potentially aliased

Can memory access m1 interfere with m2?

Potentially aliased

- Potentially aliased

- ✓ Ordered memory access

- Potentially aliased

- ✓ Ordered memory access

#### Sources of Task-Order Information

- Threads (Java)

- Low-level synchronization, difficult to analyze

#### Sources of Task-Order Information

- Threads (Java)

- Low-level synchronization, difficult to analyze

- Fork/join (OpenMP, X10, Cilk)

- Lexical scoping simplifies analysis

#### Ordering in OpenMP

```

/*A*/

//#omp parallel for

for(int i=0; i<3; i++) {

/*B*/

```

#### Ordering in OpenMP

```

/*A*/

//#omp parallel for

for(int i=0; i<3; i++) {

/*B*/

/*(*/

```

#### Sources of Task-Order Information

- Threads (Java)

- Low-level synchronization, difficult to analyze

- Fork/join (OpenMP, X10, Cilk)

- Lexical scoping simplifies analysis

- Task Libraries (Apple GCD, Microsoft TPL)

- Feature explicit task ordering

- Not much previous work here

#### Ordering in Microsoft TPL

```

Task tA = Task.StartNew(/*A*/);

for(int i=0; i<3; i++) {

tA.ContinueWith(/*B*/,

AttachedToParent);

```

#### Ordering in Microsoft TPL

```

Task tA = Task.StartNew(/*A*/);

for(int i=0; i<3; i++) {

tA.ContinueWith(/*B*/,

AttachedToParent);

/*(*/

```

#### Ordering in Microsoft TPL

```

Task tA = Task.StartNew(/*A*/);

for(int i=0; i<3; i++) {

tA.ContinueWith(/*B*/,

AttachedToParent);

B_0

/*(*/

```

#### Sources of Task-Order Information

- Threads (Java)

- Low-level synchronization, difficult to analyze

- Fork/join (OpenMP, X10, Cilk)

- Lexical scoping simplifies analysis

- Task Libraries (Apple GCD, Microsoft TPL)

- Feature explicit task ordering

- Not much previous work here

#### Sources of Task-Order Information

Threads (Java)

Not much previous work here

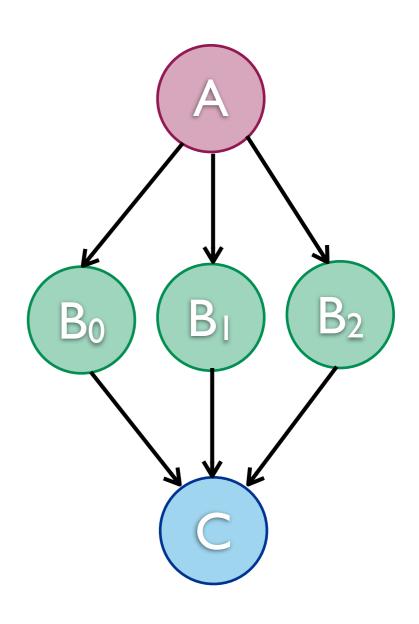

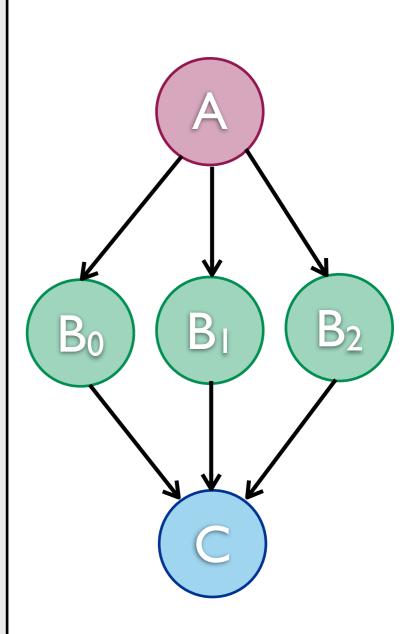

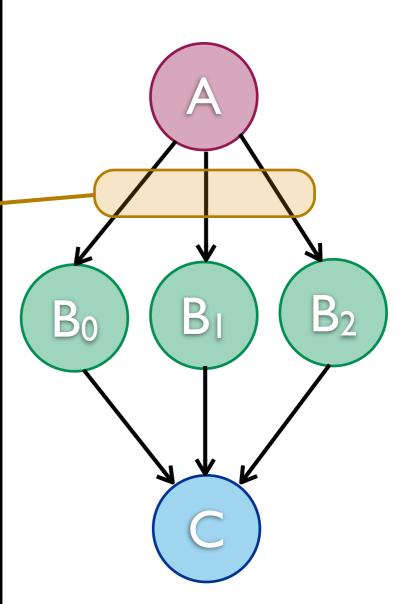

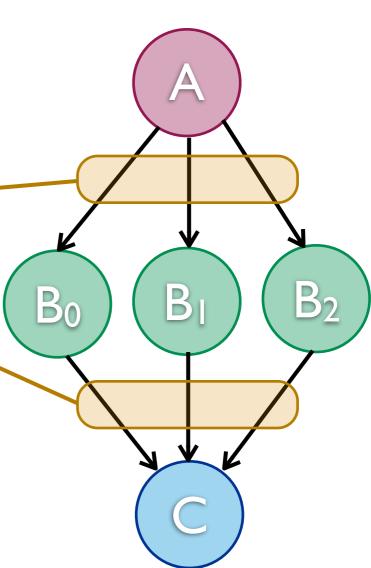

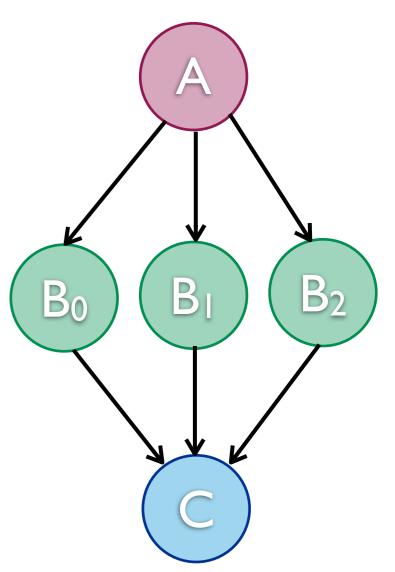

#### Our Model: Explicit Scheduling

```

Task a = schedule /*A*/;

Task c = schedule /*C*/;

for(int i=0; i<3; i++) {

Task b = schedule /*B*/;

a \rightarrow b;

b \rightarrow c;

```

#### Our Model: Explicit Scheduling

```

Task a = schedule /*A*/;

Task c = schedule /*C*/;

for(int i=0; i<3; i++) {

Task b = schedule /*B*/;

BI

```

#### Our Model: Explicit Scheduling

```

Task a = schedule /*A*/;

Task c = schedule /*C*/;

for(int i=0; i<3; i++) {

Task b = schedule /*B*/;

Bi

```

General enough to express threads, fork/join, thread libraries, ...

## Schedule Analysis

- Static bytecode analysis

- Computes relation: mayBeParallel(task1, task2)

- If !mayBeParallel(task1, task2) then task1 and task2 are guaranteed to be ordered

- 1. Extract partial schedules from source code

- Task variables plus ordering and loop information

- 1. Extract partial schedules from source code

- Task variables plus ordering and loop information

- 2. Callgraph to resolve virtual entry points for tasks

- 1. Extract partial schedules from source code

- Task variables plus ordering and loop information

- 2. Callgraph to resolve virtual entry points for tasks

- 3. Find tasks that may be created directly or indirectly without ordering

- 1. Extract partial schedules from source code

- Task variables plus ordering and loop information

- 2. Callgraph to resolve virtual entry points for tasks

- 3. Find tasks that may be created directly or indirectly without ordering

- Key insight:

- We look for unordered-ness not ordered-ness

- Unordered-ness is monotonic!

```

task T1

schedules A and B

with A → B

```

task T2 schedules A and B

task T1

schedules A and B

with  $A \rightarrow B$

task T2

schedules A and B

Ordered-ness:

```

task T1

schedules A and B

with A → B

```

task T2 schedules A and B Ordered-ness:

$@T1: A \rightarrow B$

```

task T1

schedules A and B

with A → B

```

task T2 schedules A and B

#### Ordered-ness:

$@T1: A \rightarrow B$

@T2: Ø

task T1

schedules A and B

with  $A \rightarrow B$

task T2

schedules A and B

Ordered-ness:

$@T1: A \rightarrow B$

@T2: Ø

not monotonic

B

task T1

schedules A and B

with  $A \rightarrow B$

task T2

schedules A and B

Ordered-ness:

nor monoronic  $@T1: A \rightarrow B$

@T2: Ø

Unordered-ness:

task T1

schedules A and B

with  $A \rightarrow B$

task T2

schedules A and B

Ordered-ness:

nor monoronic  $@T1: A \rightarrow B$

@T2: Ø

**Unordered-ness:**

@T1: Ø

task T1

schedules A and B

with  $A \rightarrow B$

task T2

schedules A and B

Ordered-ness:

nor monoronic  $@T1: A \rightarrow B$

@T2: Ø

Unordered-ness:

@T1: Ø

@T2: A II B

task T1

schedules A and B

with  $A \rightarrow B$

task T2

schedules A and B

Ordered-ness:

not monotonic  $@T1: A \rightarrow B$

@T2: Ø

Unordered-ness:

@T1: Ø

@T2: A | | B

## Evaluation Setup

- Bytecode-to-bytecode translation using sun.misc.Unsafe.getXYVolatile() and sun.mist.Unsafe.putXYVolatile() intrinsics

- Analyzes bytecode in SSA form

- Wala framework for analysis, Javassist for code generation

- Intel Core 2 Duo, 2.8 GHz, 4Gb RAM

- → 2 Java Threads

- Java 1.6.0 (Mac)

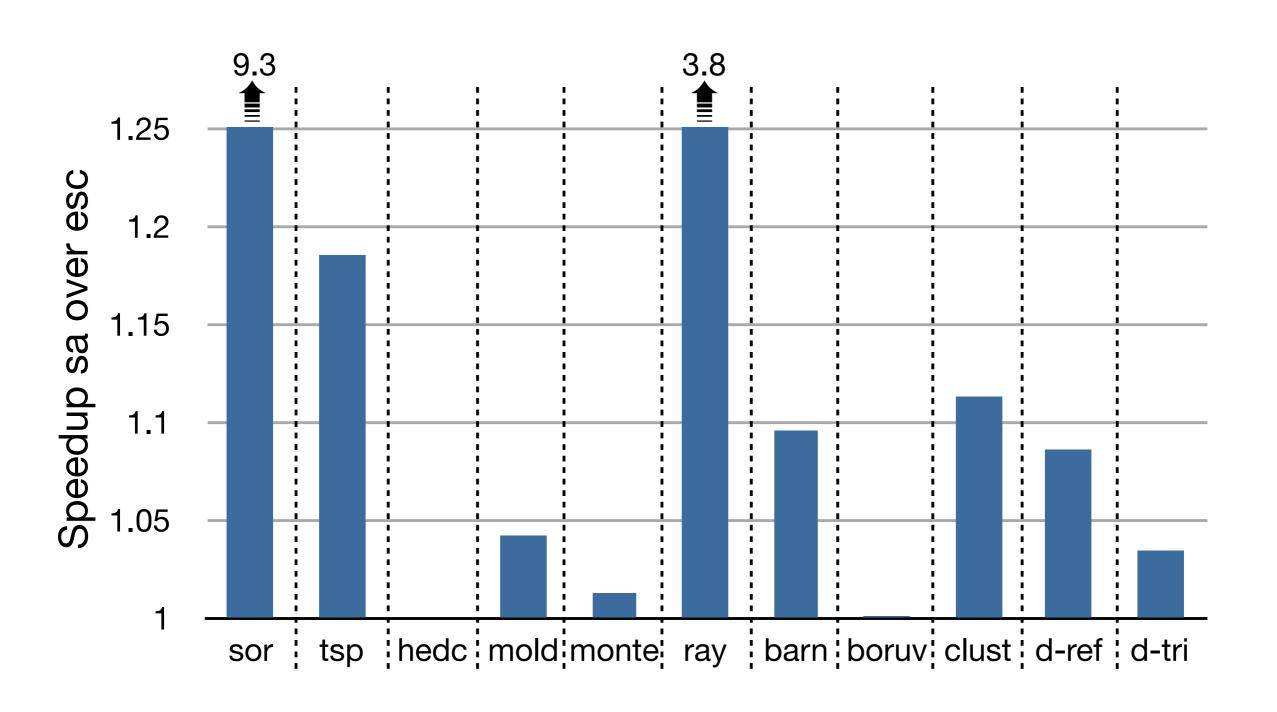

#### Benchmarks

- Erco Benchmarks: sor, tsp, hedc

- Java Grande (numeric apps): mold, ray, monte

- Lonestar (Galois): barn, boruv, clust, d-tri, d-ref

- Configurations:

- Hand-optimized (baseline)

- No optimizations (none)

- Escape analysis only (esc)

- Schedule analysis + escape analysis (sa)

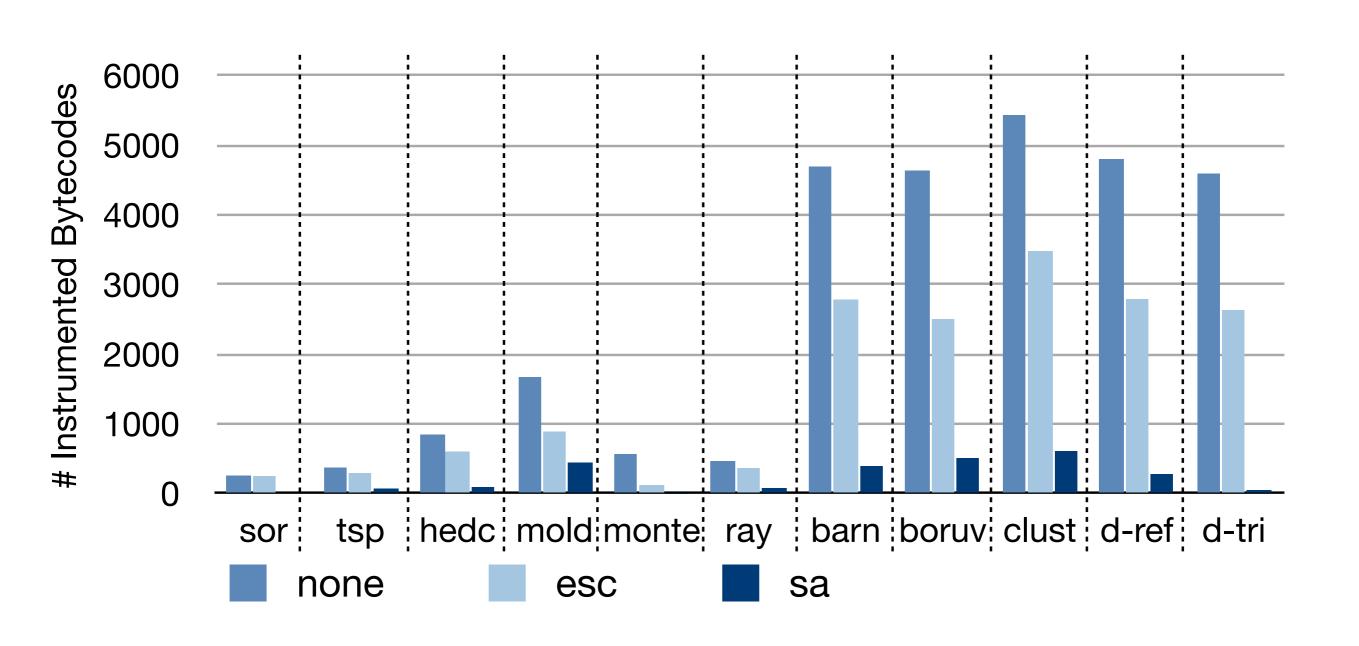

#### Instrumentation Overhead

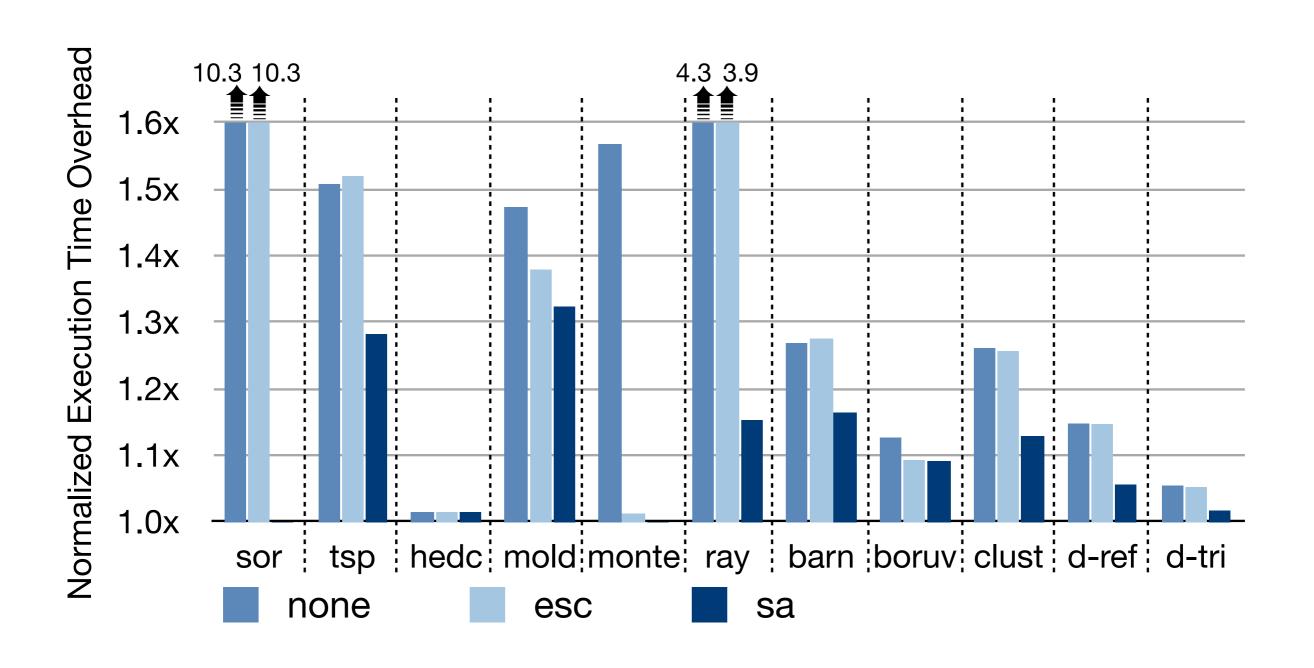

#### Execution Time

## Speedup sa vs. esc

#### Related Work

- Compiler techniques for high performance sequentially consistent java programs.

Sura et al, PPoPP'05

- A case for an SC-preserving compiler.

D. Marino et al, PLDI'11

- Efficient sequential consistency using conditional fences. C. Lin, V. Nagarajan, R. Gupta, PACT'10

- BulkCompiler: high-performance sequential consistency through cooperative compiler and hardware support. W. Ahn et al, MICRO'09

- MHP Analysis. (Agarwal et al)

## Concluding Remarks

- Optimizations for shared-memory parallel programs need task-order information to be effective

- Schedule analysis is an approach that

- can extract task-order information from realworld programs

- provides starting point for optimizations

- Modest overhead over hand-optimized sequentially consistent programs